从芯片的背面传递力量

比利时IMEC的研究人员正在将功率分布移至硅晶片的背面,以使直接递送到标准单元。

研究人员与ARM合作进行了处理器设计,在该设计中,背面发电机交付与埋藏的电源导轨(BPR)连接,这是一个埋在芯片前端的本地电力轨道。这改善了由于传统设计的阻力增加而引起的供应电压(或IR)。

然而,这是一种更复杂的能力作为专用的晶圆稀疏过程,需要与处理纳米直通式硅旋转(N-TSV)的能力结合使用,该过程将电源线从后部连接到前面的电源线

相关的IMEC文章

因此,IMEC研究人员评估了背面晶片稀疏和N-TSV制造对晶圆前面建造的缩放Si-Channel FinFET测试设备(栅极长度≥20nm)的特性的影响。使用充满钨的n-TSV来实现背面连接,这些N-TSV落在晶圆的前边的金属1垫上。

“这项工作的最重要结论是,背面的晶圆稀疏和N-TSV处理并未显示出对FinFET的性能的负面影响,除了PMOS驱动器电流的略有退化,” Naoto Horiguchi说。IMEC的CMOS设备技术。“对于NMO,在背面处理后发现了更高的迁移率和更高的驱动性(最高15%),并且没有观察到偏置温度不稳定性(BTI)降解。在这项工作中,将晶粒变细到最终的Si厚度,范围在20至370nm之间。”

在IMEC的3D集成程序的框架内开发和优化了本研究中使用的晶圆稀疏和通过N-TSV制造工艺。

“首先,在散装Si基板的顶部生长了Si/Sige层的外延堆栈。Sige层后来用作结束晶片稀疏的蚀刻层。

“然后,包括FinFET设备在内的前边是在此SI“封顶”层的顶部构建的。Cu Metal-1金属化完成了前沿处理。”他说。“接下来,晶圆被翻转过来,晶圆的'主动'前边是使用低温晶片到晶体粘结技术将第二个'载体'晶片粘合到第二个“载体” si晶圆上。现在,可以将第一个晶圆的背面稀释到Sige蚀刻层所在的位置。需要稀释至几100nm才能暴露高空比率纳米米刻度TSV。去除SIGE后,该过程通过N-TSV构图和钨填充和背面金属化完成。”

通过这种用于背面动力传递的方法,N-TSV将背面金属1电气连接到前后金属1。它们的电性能在特定的N-TSV构型(例如雏菊链)中成功验证。N-TSV可以替代降落在晶圆前沿中实施的埋入电源导轨上。这种挑战性配置的过程步骤正在开发中。

下一步:IMEC显示3D包装的背面功率

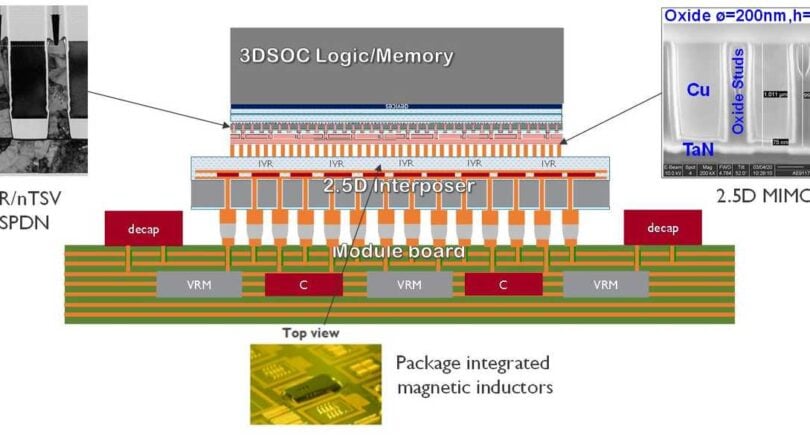

IMEC还正在寻找用于芯片上的电力输送网络以及外部芯片组件的新技术。

IMEC计划经理Geert Van Plas说:“通常,高级IC系统中的电源受到了增加的电源密度,较低的电源电压(因此,较大的电流),侵略性IR下降,电压噪声和电气移动的挑战。”。“删除功率传递以及从逻辑模具的前边到背面的功率转换可以通过特定的设计来提高系统性能。

他说:“一个示例是一种金属 - 绝缘管 - 金属电容器(或MIMCAP),它用作去耦电容器 - 一种组件,可以通过去耦合晶体管切换活动产生的噪声来稳定电压供应。”“我们已经表明,将这种被动的MIMCAP组件集成到晶圆的背面可以减少15倍的供应'弹跳'。”

通过背面传递电力也最终也会影响I/O实施,现在也应该将其移至背面。与常规的前沿I/O单元相比,背面动力输送网络的其他电容可能会影响I/O接口。VLSI的第五篇论文使用带有埋藏的动力轨道和布局选项(例如深沟式隔离)的完全背面连接来查看I/O开发路线图,以减少额外的电容。

其他关于欧洲的文章