MIPS previews its pivot to RISC-V

MIPS的主显示第一个结果the RISC-V architecture following the collapse of Wave Computing.

AI chip startup Wave bought MIPS from Imagination Technologies in 2017 but collapsed into Chapter 11 in 2021. It emerged as MIPS developing high performance processor cores based around the open RISC-V instruction set architecture. Imagination has also since gone on to launch four families of RISC-V processor cores.

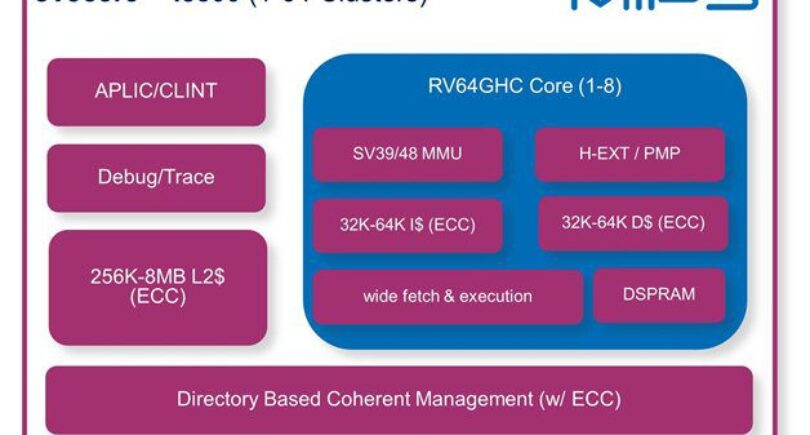

The eVocore P8700 and I8500 multiprocessor IP cores are the first results of the MIPS move to RISC-V, and are aimed at applications such as automotive, 5G and wireless networking, data centre and storage, and high-performance embedded applications.

- CEO interview: Tackling the challenges of RISC-V

- RISC-V chip designed with open source tools

- Ashling to supply toolchain for MIPS RISC-V cores

- MIPS选择和规则参考模型为RISC-V verification

- Imagination puts MIPS, Ensigma up for sale

The cores are scalable and configurable to create coherent clusters of multi-threaded, multi-core CPUs in unique combinations to meet the exact power and performance requirements. The cores are designed to provide a flexible foundation for heterogeneous compute, supporting combinations of eVocore processors as well as other accelerators, with a Coherence Manager that maintains L2 cache and system-level coherency between all cores, main memory, and I/O devices.

The use of user defined instructions (UDIs) provides the customisation while also being fully compatible with off-the-shelf RISC-V development tools and software libraries.

Both the eVocore IP cores provide support for privileged hardware virtualization, user defined custom extensions, multi-threading, hybrid debug, and functional safety.

The superscalar eVocore P8700, available in Q4 2022, combines a deep pipeline with multi-issue Out-of-Order (OOO) execution and multi-threading and can scale up to 64 clusters, 512 cores and 1,024 threads.

The eVocore I8500 is optimised for power efficiency with an in-order multiprocessing system that combines multi-threading and an efficient triple-issue pipeline.

SoCs shipping with RISC-V CPU cores are predicted to grow 73% a year between 2020 and 2027, says Semico Research, with the automotive segment projected to achieve a 69.9% CAGR during that time, although this is from a low base.

“With this transition to RISC-V, MIPS is targeting the high-performance segment of the processor market,” said Desi Banatao, CEO of MIPS. “By leveraging our differentiation in real-time features, hardware virtualization, functional safety and security technologies, we can offer compelling products for automotive, edge compute, networking and switching, and large-scale computing systems.”

“We are delighted that MIPS, one of the pioneers of RISC CPU architectures, is turning its attention to RISC-V,” said Calista Redmond, CEO of RISC-V International. “MIPS has long been used in high-end computing, an area where RISC-V is beginning to gain significant traction. MIPS is bringing to the RISC-V community a heritage of CPU innovation and new RISC-V compatible CPUs designed for flexibility and scalability.”

MIPS is also hiring hardware and software engineers in locations around the world.

Related RISC-V articles

- European processor project shows shift to RISC-V

- Imagination launches four RISC-V processor IP families

- Intel joins RISC-V, teams on foundry IP