CAN-FD IP重新设计了FPGA

新产品

|

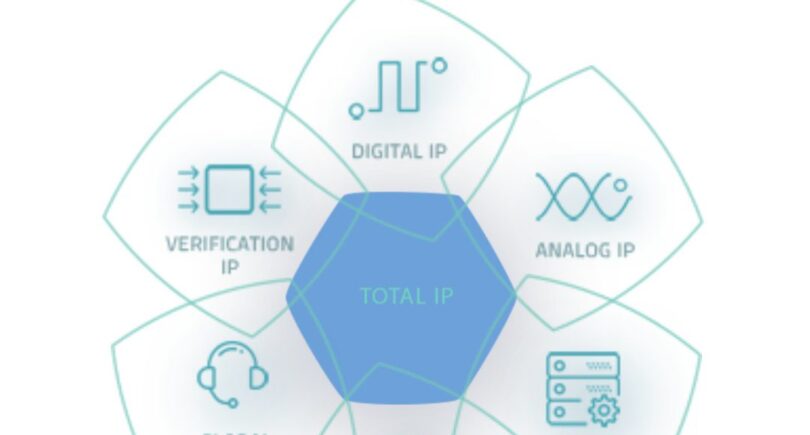

Arasan Chip Systems已重新设计了CAN 2.0的第二代CAN IP,并在FPGA设计中进行了FD规格。控制器已进行了重新研究和升级,以减少功耗和区域,这使其适合ARASAN的主要ASIC IP市场之外的FPGA应用程序。

尼克·弗莱厄蒂(Nick Flaherty)

Arasan Chip Systems已重新设计了CAN 2.0的第二代CAN IP,并在FPGA设计中进行了FD规格。

控制器已进行了重新研究和升级,以减少功耗和区域,这使其适合ARASAN的主要ASIC IP市场之外的FPGA应用程序。

第二代CAN IP控制器核心对CAN2.0进行串行通信,并且CAN FD规范,支持CAN 2.0A和CAN 2.0B协议,TT-CAN,TT-CAN,CAN-FD(ISO 11898-12.2015,Plus Pluer较早的ISO和NON-ISO,以及非ISO博世规格)。

CAN 2.0和多个设备的核心最多可达1 Mbps,旨在提高可靠性,更快的错误报告,功能高级错误管理单元,防止传输过程中的数据丢失并防止消息碰撞。

可配置的控制器内核可以使用标准的AMBA AHB/AXI接口与主机处理器集成,并具有可编程中断,数据和BAUD速率,接受过滤器和灵活的缓冲方案,以对特定应用进行微调。

Arasan的CAN IP通过多个被许可人和ASIL要求通过了合规性。

www.arasan.com/products/can-fd/

相关文章

其他关于欧洲的文章

注册到我们的新闻通讯