Silicon Labs can now offer a selection of clock generators, jitter attenuating clocks, voltage-controlled crystal oscillators (VCXOs) and XOs for 100/200/400/600G designs that satisfy sub-100 fs reference clock jitter requirements with room to spare.

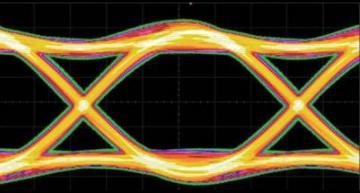

Leading manufacturers of switch SoCs have been moving to 56G PAM-4 SerDes technology for higher bandwidth 100G+ Ethernet and optical networking designs. To meet the requirements of 56G SerDes reference clocks, developers often require clocks with sub-100 fs rms phase jitter specifications. Silicon Labs now claims to be the first timing supplier to provide fully integrated clock IC solutions for 56G designs that integrate SerDes, CPU and system clocks into a single device. The same solutions will also meet the emerging 112G serial SerDes designs that will ramp in data center and communications applications in the future.

Silicon Labs’ Si5391 is a low jitter, any-frequency clock generator. It can provide all clock frequencies needed in 200/400/600G designs from a single IC while delivering sub-100 fs rms phase jitter performance. With up to 12 differential outputs, the Si5391 clock is available in frequency flexible A/B/C/D grade options. A Precision Calibration P-grade option optimises rms phase jitter performance with a 69 fs (typical) specification for the primary frequencies needed in 56G SerDes designs.

硅实验室的Si539x德西gned to meet the exacting specifications and high-performance requirements of Internet infrastructure, these ultra-low jitter clocks reduce cost and complexity for a wide range of timing applications. Si539x any-frequency jitter attenuating clocks generate any combination of output frequencies from any input frequency while delivering 90 fs RMS phase jitter performance. Si5395/4/2 P-grade devices offer typically 69 fs RMS typical phase jitter for 56G/112G SerDes clocking applications.

The Si56x Ultra Series VCXO and XO family are customisable to any frequency up to 3 GHz. The Si56x oscillators are available with single, dual, quad, and I2C-programmable options in 5 mm x 7 mm and 3.2 mm x 5 mm packages.

Silicon Labs also offers