Leonardo一直在使用Mentor公司的Questa SystemVerilog验证工具,作为通用验证方法(UVM)框架的一部分,与Questa验证IP (QVIP)一起用于航空电子雷达接口的验证和验证(V&V)。将UVM框架、QVIP和Verification Run Manager整合到基于Jenkins软件的环境中,在工具箱中提供了更多的价值,因为它允许修改后的设计的自动再验证。

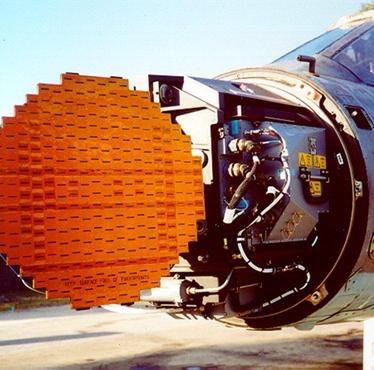

电子扫描阵列雷达系统包含多个中央处理单元(cpu)和fpga,分布在几个子系统上,fpga实现控制、数字信号处理(DSP)和通信功能。“设计这样一个复杂的系统是一项艰巨的任务,尤其是考虑到今天快节奏的市场所要求的紧凑的日程安排,”Iain Wildgoose说,他是Leonardo机载和空间系统部门的工程、雷达和高级目标副总裁。“UVM框架和QVIP提供的重用和可伸缩性,以及Mentor顾问和应用工程师提供的对采用过程的支持,是成功设计和集成的关键因素。”

Mentor QVIP为40多个标准协议和1700个内存设备提供了一个验证IP库。QVIP包括检查和覆盖,加上一套全面的刺激序列的协议。采用QVIP IP作为标准接口,使Leonardo能够专注于公司设计的独特细节。QVIP和UVM框架——一组层叠在UVM之上的基类——使Leonardo能够在短时间内显著增加代码覆盖率。

通过将这个任务抽象到一个更高的层次,使用UVM框架减少了创建测试台以及解释测试台结果所需的时间。Leonardo能够跨项目部署Questa,以加速测试平台的开发和有效的覆盖关闭。在这些初步的成功之后,Leonardo现在正在将UVM框架部署到公司的其他项目中。