英伟达已经使用强化学习和其他类型的人工智能来提升其标准单元在高级工艺节点5nm和3nm的自动化布局。

在12月的设计自动化会议上,Mark Ren的团队在一篇预印本论文中,Matt Fojtik和Brucek Khailany开发了一种名为NVCell的自动标准单元布局生成器,它可以在一个先进的技术节点上,为行业标准单元库中92%的单行单元生成同等或更小面积的布局。

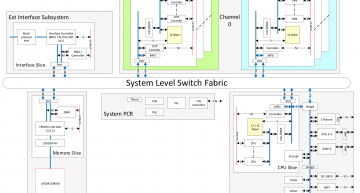

由于复杂的设计规则,先进技术节点的高质量标准单元布局自动化在当今行业仍然具有挑战性。强化学习(RL)用于解决路由过程中违反设计规则的问题,提高单元放置的效率,从而使模具更小,节约成本,提高性能。

研究人员使用了一种基于模拟退火算法的设备放置和引脚分配,该算法同时执行设备配对和放置,以找到高质量的放置。

相关文章

- 三星铸造厂磁带出3nm GAA芯片

- 苹果、英特尔率先采用台积电的3nm制程

- 为ARMv9设计的3nm物理IP磁带

- 专利扼杀了创新吗?美国专利局正在问这个问题

- 欧洲将审查英伟达收购arm的交易

- 在英伟达(Nvidia),数据中心业务超过了游戏业务

基于RL的放置算法加快了使用模拟退火的放置速度。在训练后84%的细胞测试中,这能够产生与基于模拟退火的砂矿相同质量的布局。这与基于RL的方法相结合,以修复标准单元上现有路由的DRC错误。模型在一个标准单元上训练,可以转移到Nvidia库中的所有标准单元

基于机器学习的可路由性预测器有助于预测给定布局的可路由性,在额外的9.5%的单元上生成竞争性布局。

在路由流程中采用遗传算法查找最小路由,优化DRC误差。与基于RL的DRC固定器一起,它发现了可路由的DRC-clean单元布局,与专家布局工程师找到的最佳布局相比,其宽度更小

其美妙之处在于,放置的标准单元格越多,算法的表现就越好,因为模型可以进一步对每个单元格进行重新训练,以改善结果。在5纳米和3纳米设计中有数百万个标准电池,这将迅速提高芯片布局的质量。

当然,这些算法是在英伟达的图形处理器单元上运行的,在这种情况下,训练是在英伟达V100 GPU上进行的。

相关文章

eeNews Europe的其他文章