芬兰SoC Hub联盟发布了其首个用于物联网和Edge AI应用的芯片设计系统。

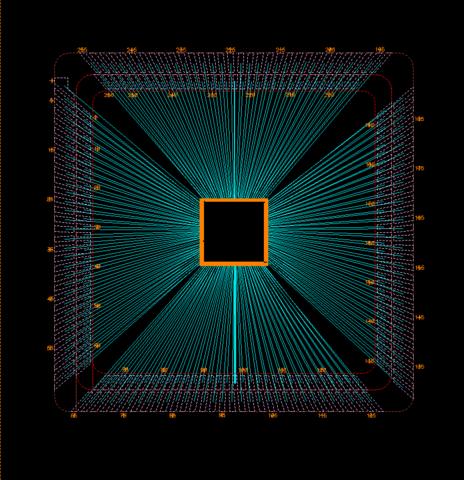

该镇流器芯片是台积电采用22nm超低漏液工艺生产的三片芯片中的第一款,适用于物联网和Edge应用。镇流器包含几个不同的RISC-V CPU核,一个数字信号处理器,AI加速器,类似传感器的接口和FPGA的扩展接口。一个完整的软件堆栈——包括驱动程序,软件开发工具和芯片调试支持——也已经实现,芯片同时支持实时操作系统和Linux。

该项目的合作伙伴将集中在提高SoC的设计,自动化和性能的下一步。第一个三个芯片由财团开发将随时为部署在2022年年初。

芬兰的SoC中心旨在促进SoC设计技术在欧洲和提升芬兰的竞争地位。该SoC枢纽举措,去年推出的,由坦佩雷大学和诺基亚,而是由合作伙伴开展合作,创造活动的协调,远远超出常规研究项目的范围。财团的其余部分包括CoreHW,VLSI解决方案,SIRU革新,TTTech公司Flexibilis,Procemex,Wapice和卡哥特科。

坦佩雷大学SoC设计实践教授Ari Kulmala说:“SoC的开发采用了与工业生产相同的方法,如可测试性设计、广泛验证和专注于系统级集成而不是单个模块。”

根据Kulmala的说法,该芯片也可以由外部利益相关者进行测试,因为它包含了一个开发工具包,而且它可以集成到其他广泛的系统中。

之一的SoC枢纽工程的主要目标是让新的想法快速成型,例如,在物联网(IOT),机器学习和5G和6G技术在硅互联网。

“这是一个很高兴的工作与该SoC中心团队。他们一直非常快,开发芯片,和工作质量得到了顶级,”巴斯Dorren,业务发展总监imec.IC链接,比利时R&d中心的一部分说。

相关文章

另外两个芯片在未来两年内完成设计

“工作的一个很大的已经做了,使大学和企业合作伙伴之间的无缝协作。一些早期的职业生涯的研究人员参与设计镇流器,因此不得不申请,他们从他们的研究获得在工业项目中的知识的机会,”蒂莫Hämäläinen,坦佩雷大学计算机科学部的负责人说。

除了发展SoC外,项目的第一阶段也是一项主要工作,包括建立联盟和编制必要的软件和许可证协议。在这个由“芬兰商业”资助的项目中,三个soc将在2023年底建成。芯片的用例将与项目联盟一起规划。

“在项目的下一阶段,我们将能够更专注于系统级芯片的系统学,自动化和性能。尽管已经取得了我们的第一个目标,我们继续前进的时候了。投资于SoC开发的时间是现在,不是明天,”Hämäläinen说。

相关文章

关于Eenews欧洲的其他文章