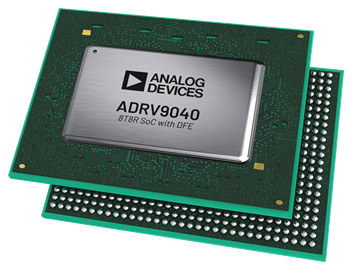

Analog Devices的目标是通过其最新的软件定义芯片系统将fpga从5G无线电设计中剔除。

RadioVerse SoC提供零中频射频信号处理,具有扩展的数字功能和射频容量,提高5G RU性能和能源效率.

ADRV9040是新RadioVerse SoC系列中的第一款产品,提供8个400MHz带宽的发射和接收通道,可调范围从650 MHz到6GHz。该13W芯片集成了载波数字上变频器(CDUC)、载波数字下变频器(CDDC)、波峰因数降低(CFR)和数字预失真(DPD)。ADI表示,这种扩展的信号处理可以消除对现场可编程门阵列(FPGA)的需求,减少了热足迹,以及系统的总尺寸、重量、功耗和成本。

芯片中的DPD算法使用先进的机器学习技术开发,并与主要的功率放大器(PA)供应商密切合作优化,以减轻设计负担并提供最佳的宽带性能。算法在4G和5G使用案例中进行了全面测试和验证,包括各种PA技术类型,如氮化镓(GaN)。此外,ZiF无线电架构简化了射频滤波和信号链组件,减少了RU成本和频段和功率变体设计的开发时间。

相关文章

- 机器学习提高OpenRAN 5G频谱效率

- ADI将RadioVerse技术用于4G到5G

- 宽带射频收发器降低了基站成本

- NEC将Xilinx AI fpga用于下一代5G无线电设备

- 首款用于5G RAN的50G PAM4 DSP芯片组

三星电子副总裁兼硬件研发集团网络事业本部长李东根(音)表示:“三星电子和ADI长期以来一直致力于支持5G在全球市场的快速部署。”“我们对ADI新SoC的成功推出感到兴奋,因为我们期待这一前沿技术将为消费者带来更好的5G体验。我们期待扩大与ADI的合作。”

随着全球网络运营商竞相部署5G基础设施,对节能RUs的需求正在迅速扩大。随着无线需求的指数级增长,能源效率是运营商的一个关键指标,因为他们寻求减少碳足迹,同时扩大网络容量。与其他替代方案相比,新的RadioVerse SoC系列需要非常低的功耗,并实现了先进的算法,提供最佳的RU系统效率。

“RadioVerse soc的设计是为了优化整个无线电解决方案,而不仅仅是单个组件或接口,”Analog Devices的无线通信副总裁Joe Barry说。“每一代都提供了扩展的能力、带宽和性能,同时提高了整体RU效率。这一新的radiooverse SoC系列在信号处理方面取得了多项进步,以满足5G的苛刻需求,从而向前迈出了一大步。”

OpenRAN相关文章

- 盒装开源5G使用16核AMD处理器

- 英国寻求建立自主的开放式RAN供应链

- OpenRAN用于英国5G AI智能城市部署

- 2800万英镑用于英国5G OpenRAN项目

- “德国制造”用3亿欧元购买OpenRAN

- 首个5G多厂商OpenRAN智能控制器演示

eeNews Europe上的其他文章