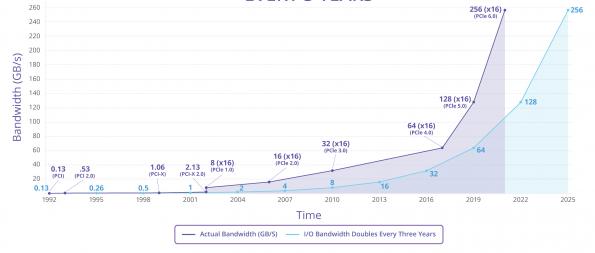

Avery Design Systems为LPDDR5和HBM3的PCIe 6.0和高级内存技术推出了本机FPGA速度适配器,以及对HBM3接口标准的验证支持。Rambus还使用Avery的HBM3内存模型来验证其HBM3 PHY和控制器子系统

PCIe 6.0为速度适配器提供的是与S2C EDA的合作伙伴关系和其Prodigy逻辑矩阵LX2系统,用于高性能ASIC / SOC原型设计,并启用最新数据中心,NVME和嵌入式存储和AI的系统验证/ ml集SOC设计,其包含最新的高速互连和内存技术。

相关文章

Avery speed adapter加速软件开发、硬件验证和系统验证,使FPGA原型能够与本地系统平台集成,允许验证以实际系统运行速度执行。这种方法克服了系统soc的多fpga表示固有的性能限制,并且缺乏对最新一代PCIe或内存技术的支持,”英国图克斯伯里Avery销售和营销副总裁Chris Browy说。通过与S2C的合作,我们解决了大规模SoC设计中不断增加的复杂性和性能要求,并提供了准确和及时的验证方法。”

“FPGA原型设计本质上是关于高性能验证的。高性能的质量不仅加快了设计周期,还可以通过与真实数据的交互来捕获硬件和软件漏洞,”S2C销售和营销副总裁Ying Chen表示。“逻辑矩阵LX2是一个高密度FPGA原型平台,包含8个Xilinx VU19P FPGA,旨在满足复杂SoC设计中对容量和性能的需求。通过与Avery的合作,我们的客户现在可以轻松地验证最新一代的PCIe和内存接口。”

Avery支持一系列系统级验证和硬件加速解决方案,这些解决方案补充了其全系列领先的SystemVeriLog / UVM验证IP。这包括使用QEMU和ARM快速模型以及针对任何Xilinx FPGA板的Simaccel协同仿真软件工具和系统IP的虚拟主机和嵌入式平台共模。