现场可编程门阵列(fpga)的起源可以追溯到20世纪80年代,从可编程逻辑器件(pld)发展而来。从那时起,FPGA资源、速度和效率迅速提高,使FPGA成为各种计算和处理应用的首选解决方案,特别是当产量不足以抵消特定应用集成电路(ASIC)的开发成本时。

fpga已经发展到这样的程度,它们也在大规模部署中找到了归宿。例如,在2013年的一个试点项目中,微软成功地用fpga加速了必应搜索引擎的运行,之后,微软将fpga服务器的使用扩展到了云数据中心。

FPGA电源系统要求

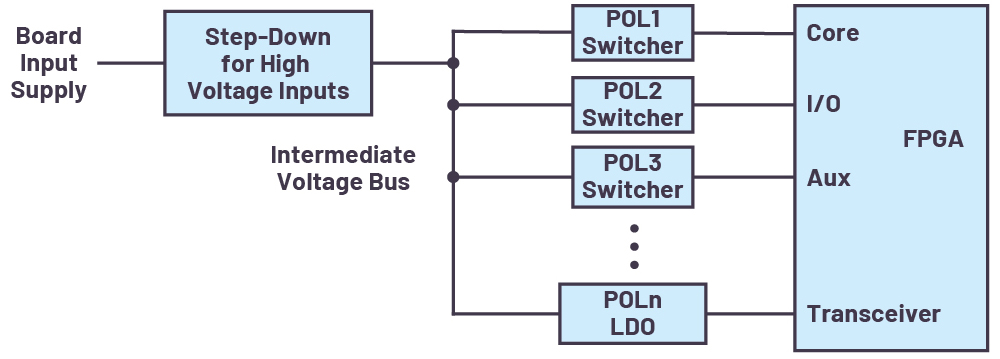

fpga需要几个不同的低压电源轨,每个都有自己的电压和电流规格,以驱动其内部核心逻辑、I/O电路、辅助逻辑、收发器和存储器。这些轨道可能需要按特定的顺序打开和关闭,以避免损坏FPGA。点负载(POL)稳压器降低板的较高的输入电源电压到多个较低的轨道电压所需的FPGA。当功率转换效率至关重要时,开关稳压器被用作POL稳压器,而线性稳压器——例如,低差(LDO)稳压器——被用于噪声敏感电路,如锁相环和收发器。

电源(如12v、24v、48v)降至

供给POL调节器的中压母线

FPGA。

典型的板输入电压为5v、12v、24v和48v,而FPGA轨电压范围在1v以下到3v左右。高输入电压(12 V、24 V、48 V),可能需要额外的降压来生成一个中间电压总线为波尔监管机构(见图1)。在FPGA rails中,核心供应需要的最低电压(在或低于1 V)和最高精度(±3%或更好),根据FPGA资源利用率的不同,电流水平在几十安培。

为了防止逻辑错误,电源变化需要限制在几十毫伏,这是由FPGA轨道公差规范所规定的,不仅在直流条件下,而且在FPGA电流瞬变期间。电源的直流精度越差,在瞬态条件下维持可接受的供电电压所需的旁路电容越大。例如,假定磁芯电压公差为±3%。使用±1%的精确直流电源,可以留下±2%的瞬态余量。另一方面,不太精确的±2%直流电源留给瞬态的空间(±1%)更少,比以前的情况需要更多的旁路电容。