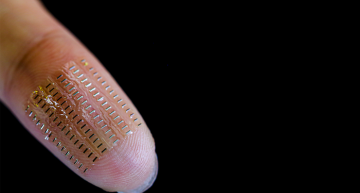

Esperanto Technologies is showing details of an AI accelerator chip with over 1000 RISC-V cores designed in the US, Spain and Serbia.

The ET-SoC-1 AI inference chip is designed to be the highest performance commercial RISC-V chip says founder and executive chairman Dave Ditzel, a former founder of Transmeta, VP at Intel and Sparc CTO at Sun Microsystems speaking at the Hot Chips conference in California.

The chip is designed to operate at under 20W using 1088 of the ET-Minion 64bit processor cores each with its own custom vector / tensor unit alongside four high performance out-of-order RISC-V processor cores called ET-Maxion alongside a high-performance memory system with over 160Mbits of SRAM.

The dual thread ET-Minion core runs from 300MHz to 2GHz and has an in-order pipeline with low gates/stage to improve MHz at low voltages and is optimized to enable low-voltage operation. The vector/tensor unit handles a 512bit wide integer per cycle and 128 8-bit integer operations per cycle, accumulates to 32bit Integer. The cores can handle a 256bit wide floating point per cycle with 16 32bit single precision operations per cycle. It also adds new multi-cycle Tensor instructions that can run for up to 512 cycles (up to 64K operations) with one tensor instruction. This reduces instruction fetch bandwidth and reduces power as the RISC-V integer pipeline put to sleep during tensor instructions.

The Minions are connected in ‘neighbourhoods’ of eight, grouped into ‘shires’ of 32 cores with 4Mbits of SRAM that ar, with the shires connected via a mesh network.

The low power allows six Esperanto chips and 24 DRAM chips to fit into a 120W PCIe card in a data centre rack. This allows a single ML model on one accelerator card to access up to 192 GB of low-cost LPDDR4x DRAM with up to 822 GB/s of memory bandwidth. Over 6K cores with 12K threads handles memory latency on 96 memory channels.

Related articles

- CEO Interview: We develop new AI processors on the open RISC-V architecture

- Esperanto raises funds for AI superchip

- UltraSoC aids design of Esperanto processor chip

Esperanto is headquartered in Mountain View, California with engineering sites in Portland, Oregon, Barcelona, Spain, and Belgrade, Serbia.

The company also announced that it expects to begin an Early Access Program for qualified customers later this year.

“I’m impressed with the energy efficiency and memory bandwidth of this new AI chip, which is the first and fastest RISC-V design we have seen for high-performance data centre workloads,” said Karl Freund, founder and principal analyst at Cambrian AI Research. “In addition, there are significant benefits to the programmer of using standard RISC-V cores, including flexibility and the ability to easily optimize code.”

“Esperanto’s chip is focused on high throughput with energy efficiency,” said Rich Wawrzyniak, principal market analyst at Semico Research Corporation. “With so many RISC-V cores operating in unison, the ability to process very large models operating using their low-voltage approach really delivers on the performance per watt.”

Other AI accelerator chip articles

- IBM shows its first dedicated AI inference chip

- Intel shows engineering silicon of its biggest ever 'chip'

- GraphCore joins €2.6m project for real world AI

- Graphcore, SiPearl team for AI supercomputer

- Graphcore signs strategic deal with Atos

Other articles on eeNews Europe