Astera Labs开发了第一个实现最新CXL 2.0内存互连标准的芯片。

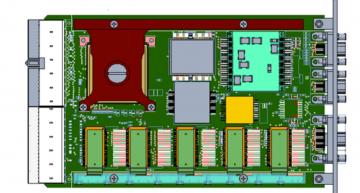

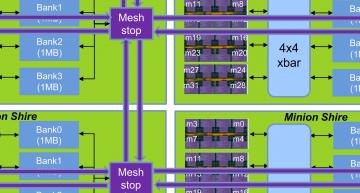

Leo内存加速器平台使用CXL (Compute Express Link) 1.1/2.0标准连接分解内存和处理器池、AI加速器和智能I/O设备。Leo克服了处理器内存带宽瓶颈和容量限制,同时为大型企业和云服务器部署提供内置舰队管理和诊断。

Astera实验室首席执行官Jitendra Mohan表示:“对于超大规模的数据中心来说,CXL是真正的游戏规则改变者,它能够实现内存扩展和池化功能,以支持以数据为中心的可组合计算基础设施的新时代。”“我们与领先的处理器供应商、系统oem和战略云客户同步开发了Leo SoC平台,以释放下一代内存互连解决方案。”

由于对更多内存和人工智能的需求,CXL在云计算中的应用正在增长。第一个支持cxl的内存模块于今年5月开始发货。

Leo是业界第一个实现CXL的CXL SoC。内存(CXL.mem)协议,允许CPU通过PCI Express 5.0通道访问和管理cxl附加的DRAM和持久内存。这样可以更有效地利用集中的内存资源。

Astera利用其使用CXL retimers的经验,将内存带宽提高到每lane 32 GT/s,容量提高到2TB(延迟),为云规模操作提供服务器级别的可靠性和可用性。CXL 2.0增加了对交换、持久内存和安全性的支持,以及对内存池的支持,以最大限度地提高内存利用率,减少或消除对过度供应内存的需求。

英特尔技术计划总监Jim Pappas表示:“CXL的引入提供了在cpu和加速器之间创建统一、一致的内存空间的关键能力,这一创新将彻底改变未来数年数据中心服务器架构的构建方式。”“Astera实验室的Leo CXL内存加速器平台是英特尔生态系统实现主机和附加设备之间共享内存空间的重要推动因素。”

AMD客户兼容性主管Michael Hall表示:“AMD认识到CXL为异构计算带来的巨大价值,以满足行业对通过资源分解增加计算能力和更快数据处理的需求。”像Astera Labs的Leo内存加速器平台这样的解决方案对于AMD处理器、加速器和内存扩展之间的紧密耦合至关重要。”

ARM战略部门高级总监John DaCosta表示:“为了继续促进异构计算的快速增长,我们需要消除诸如跨企业、超大规模、存储和加速器应用程序的扩展内存和高速互连的成本等障碍。”ARM将CXL视为这一领域的重要驱动力,Astera Labs的新平台将利用基于ARM的技术帮助解决云计算和边缘计算数据中心的这些需求。”

CXL联盟主席Barry McAuliffe表示:“Astera Labs一直是CXL联盟的重要成员,在实现异构计算架构的连接方面贡献了其专业知识。“我们很高兴地看到Astera Labs推出了第一个CXL内存扩展和池化解决方案,以支持快速扩展的CXL生态系统。”

相关文章

eeNews Europe上的其他文章