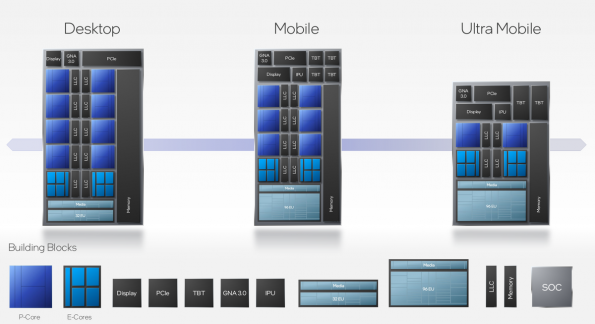

英特尔的下一代台式机芯片代号为Alder Lake,是该公司第一款集成了两种核心类型的混合体系结构——高性能核心和高效核心。这与ARM的big.little方法类似,该方法使用了一个小型内核,与一个更大、更高性能的内核一起优化,以实现低功耗、低性能。这两个内核可以根据上下文运行相同的代码,避免了调度程序将任务分配给多个内核的问题。传统上,这是多核芯片设计的系统级性能的限制因素。

Intel的混合方法基于线程,带有线程控制器。这是一种改进的调度技术,增加了对内核的更多监控,以确定上下文。Intel希望这种增加的监控与线程方法和三个独立的结构相结合,将避免潜在的性能瓶颈。

计算结构可支持高达1Tbyte/s的速度,即每个核心或群集100 GBps,并通过最后一级缓存将核心和图形连接到内存。这具有较高的动态频率范围,并能够根据实际结构负载动态选择延迟与带宽优化的数据路径。它还可以动态根据利用率,以逻辑方式将最后一级缓存策略调整为包含或非包含。

相关手臂大。小文章

I/O结构支持高达64 GBps的速度,可连接不同类型的I/O以及内部设备,并可无缝更改速度,而不会干扰设备的正常操作,选择结构速度以匹配所需的数据传输量

内存结构可以提供高达204 GBps的数据,并动态调整其总线宽度和速度,以支持高带宽、低延迟或低功耗/的多个操作点。

它们连接不同类型的处理器核,由线程控制器控制。这是直接内置到硬件中的,并提供对内核状态和线程指令组合的低级遥测。线程控制器是动态和自适应的,它根据实时计算需要调整调度决策,而不是使用编译时确定的简单静态规则,这允许操作系统在正确的时间将正确的线程放在正确的内核上。

传统上,操作系统将根据有限的可用统计数据(如前台和后台任务)做出决策。Thread Director使用硬件遥测将此时需要更高性能的线程定向到正确的性能核心。通过在粒度级别监控指令组合、核心状态和其他相关微体系结构遥测,操作系统可以做出更智能的调度决策

Intel还扩展了“PowerThrottling”API,使用EcoQoS分类通知调度程序线程是否更喜欢节能,以便在高效内核而不是性能内核上调度线程。

下一步:高效核心vs性能核心